当我们讨论芯片制造的时候,我们造的到底是什么?

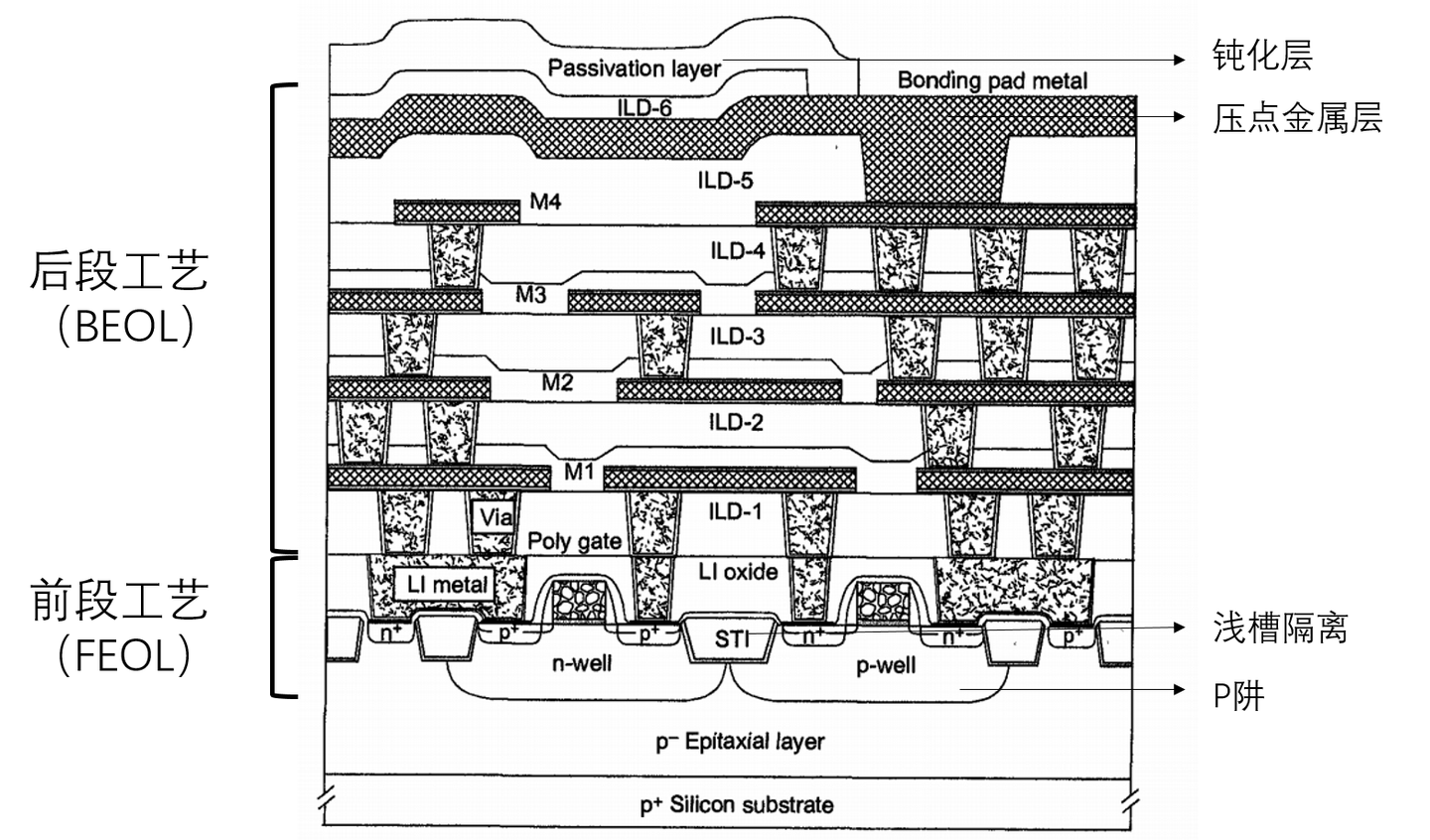

下图就是一个逻辑芯片剖面图的典型结构。

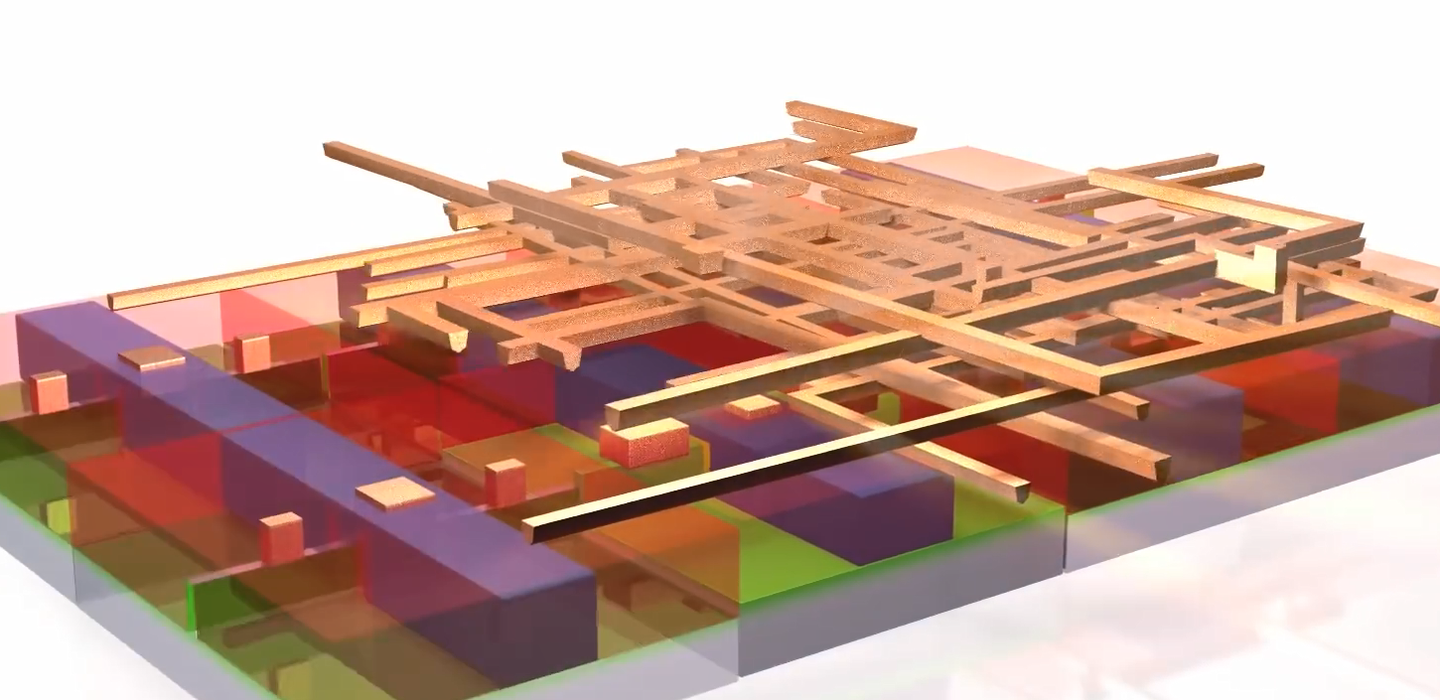

芯片结构的3D示意图

芯片结构的3D示意图

从本质上来讲,芯片的内部物理结构就是一个具有多层图案结构的堆叠,并且层与层之间实现了有序互连。

从材料来讲,每层结构的组成无外乎为半导体材料、导体材料、绝缘体材料。

按照工艺段的顺序,大体上可以分为前段工艺(FEOL)和后段工艺(BEOL)。

简单地理解,FEOL部分主要负责形成CMOS晶体管结构,BEOL部分负责进行金属布线。

实现这些结构主要利用几大工艺模块轮番上阵、相互配合:光刻、刻蚀、薄膜沉积、CMP(化学机械抛磨)和Implant。篇幅关系,每一个工艺模块就不一一介绍了,可以看一下这个视频,对这几大工艺模块就有了初步的认识。

下面就按照芯片制造工艺顺序介绍一下芯片内的主要结构。

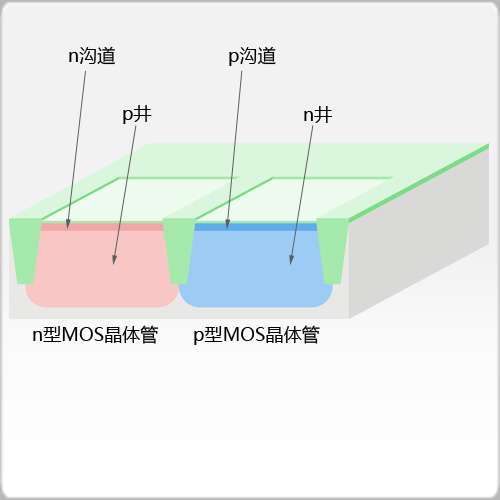

步骤1:阱以及隔离结构的形成

一般用双阱工艺定义nMOS和pMOS晶体管的有源区。所谓的双阱,就是一个n阱一个p阱。可通过追加掺入不同的杂质及不同浓度的剂量來分别制作不同电压/特征的晶体管。

阱形成后,利用浅槽隔离(STI,Shallow Trench Isolation)工艺将n阱p阱进行物理隔离。

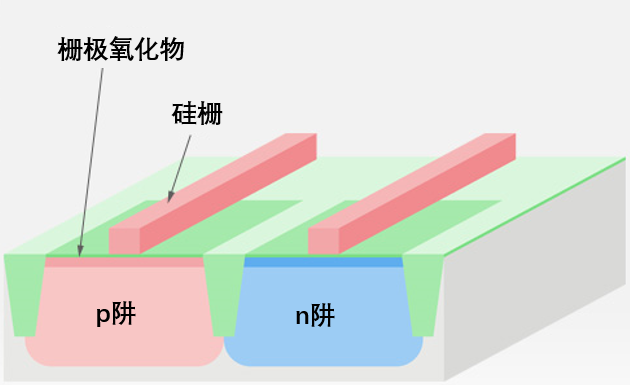

步骤2:栅氧以及硅栅结构的制造

CMOS晶体管制作中最重要的一步,多晶硅栅的宽度通常是最重要的CD(关键尺寸)线宽。这是因为,硅栅形成的尺寸也会对晶体管的性能产生重要影响,栅氧对晶体管的性能及可靠性影响也很大。

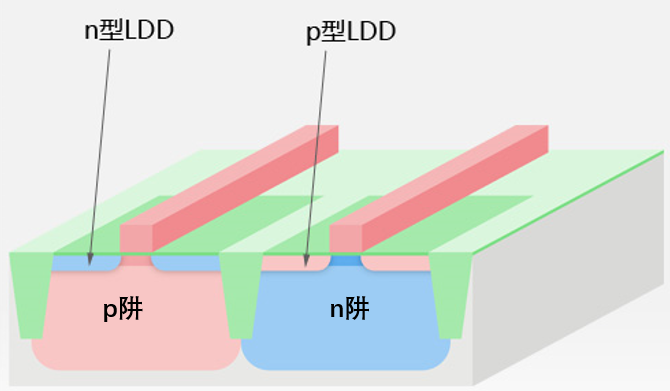

步骤3:LDD结构的制造

LDD,即为轻掺杂漏注入。晶体管中沟道长度的减小增加了源漏之间电荷穿通的可能性,并且存在短沟道效应。LDD的存在,就是有效防止这两种负面作用。

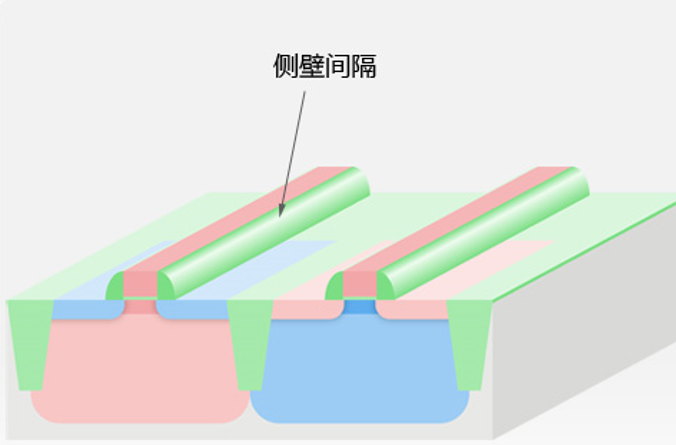

步骤4:侧壁间隔的制造

侧壁的制造是为了在栅极的侧壁上形成氧化膜,在电子学上的作用是防止在更大剂量的源漏注入后,源和漏过于接近导电沟道而可能发生源漏穿通。

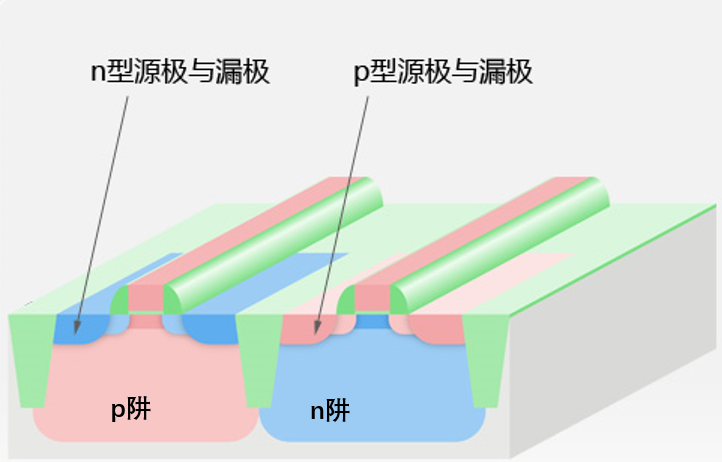

步骤5:源和漏的形成

在n阱和p阱区域内形成各自的源极和漏极。电源的连接方向决定哪一端是源极或漏极。

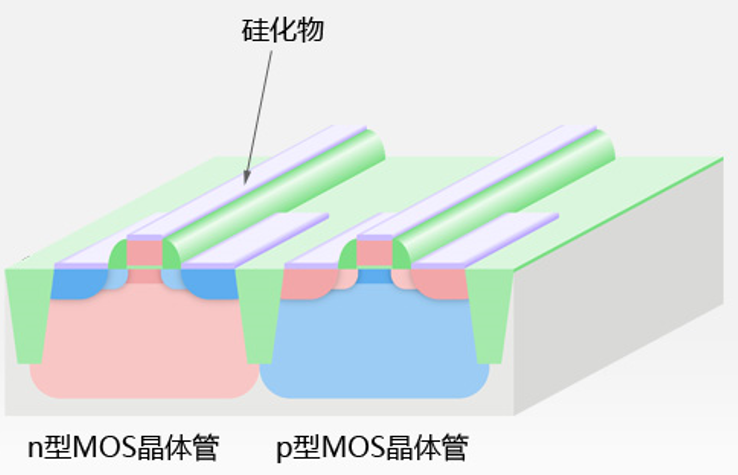

步骤6:金属接触区域硅化物的形成

形成一个薄层,成分是金属与Si的硅化物。这个硅化物是金属与Si在反应过程中得到的,并不是直接沉积得到的。对MOS的三个电极即栅极、源极、漏极进行硅化后,可以降低对金属布线层的电阻。同时,也可以降低各自电极滋生的电阻。

钛一般是制作金属接触的理想材料。

以上是FEOL,下面进入BEOL布线。

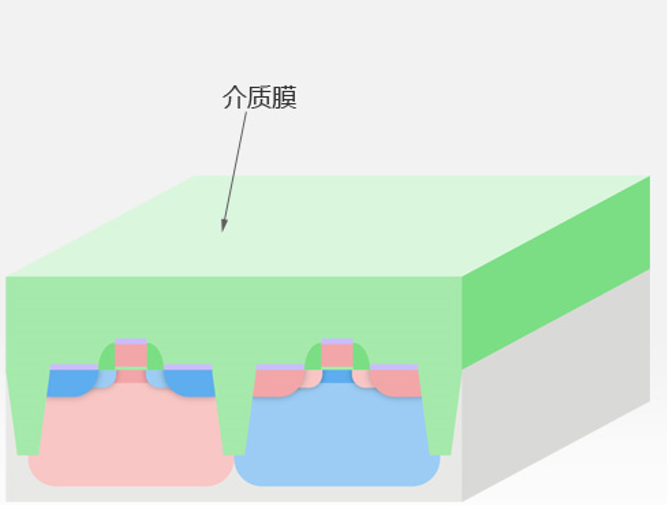

步骤7:介电层的形成

这个不需要过多解释,后段制程中,无论是金属线还是金属通孔都是分布在介电材料中。在每层金属布线前,需要分别将每层的介电层做好,使用的方式一般是CVD(化学气相沉积)。

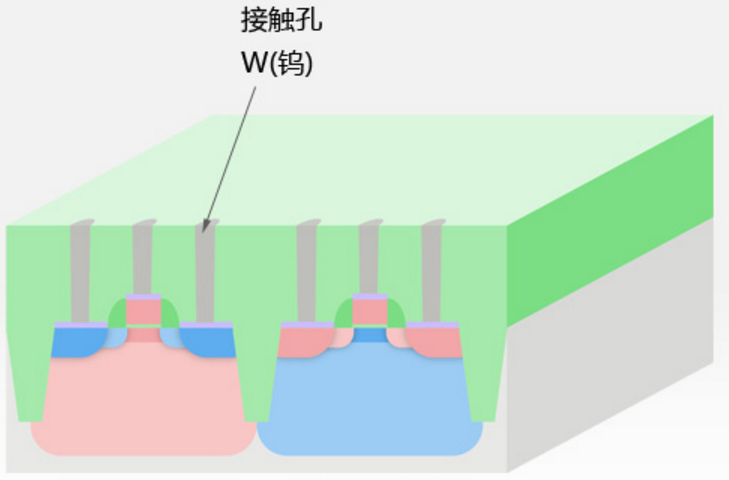

步骤8:通孔的形成及其金属填充

通孔是指向下贯穿的圆孔,也成为接触孔。层与层之间的导线链接需要通孔。形成通孔以后,在通孔内沉积金属。最常见使用的金属是钨、铜。

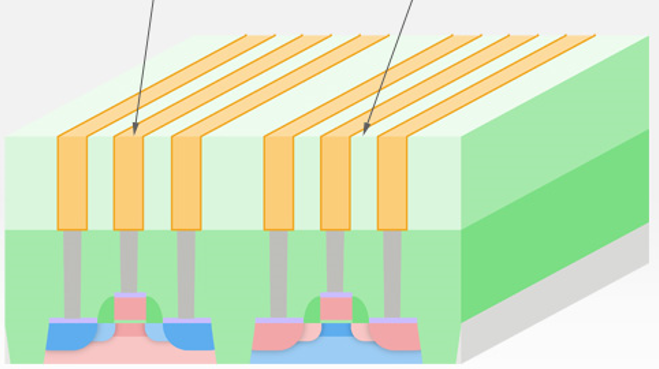

步骤9:横线的形成及其金属填充

这部分工艺的目标结构是金属连接线的横向部分。一般使用大马士革工艺实现,这个名字取自于前叙利亚大马士革一位艺术家发明的一种技术,金属线镶嵌在介电层内部,类似于首饰或者艺术品的镶嵌,故而得名。

需要说明的是,上述通孔和横线的形成需要重复多次,以获得多层金属连接结构。

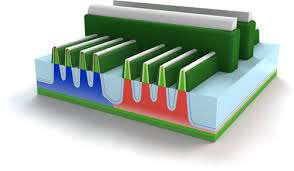

另外,随着工艺的进步以及芯片性能要求的提高,上述芯片内的典型结构开始出现一些衍生形式,比如逻辑芯片CMOS结构使用的FinFET的形式。

FinFET示意图

FinFET示意图

此外,对工艺要求的尺寸精度要求逐渐提高,图案的层数也越来越多。

总之,芯片制造就是盖一座特别精细的楼这个楼,需要在特定的位点有特殊的图案和材料。

最后,在网上找到一个Intel Ivy Bridge 22nm FinFET 工艺芯片流程的动画视频,帮助大家理解。

- 上一篇:半导体厂商如何做芯片的出厂测试? 2021/6/26

- 下一篇:为什么"电路"要铺满整个晶圆? 2021/6/26